First Seen

2025-08-20T20:19:24.691314+00:00

simple-description (qwen3.5_2b-q8_0)

From the perspective of embedded systems, this diagram is a humorous "status update" illustrating how modern architectures integrate different types of processors (like Arduino, STM32, and Raspberry Pi) into a single unified system. It serves as a visual poster for engineers sharing their project details or architecture code. For someone who cannot see it, the image looks like a giant schematic board featuring icons for hardware like 'Raspberry Pi 4' and an 'FPGA', connected by lines labeled with frequencies such as '80 MHz' and '2 MPS', culminating in the bottom right corner where a black box is labeled 'AI chip Muhammad Rizwan'.

detailed-analysis (gemma3_27b-it-q8_0)

Okay, let's break down this image – a meme illustrating an ESP32 co-processor architecture – through the lens of microcontrollers, and then explore potential theoretical interpretations. Given the technical nature of the image, some theoretical frameworks will be more applicable and insightful than others.

Visual Description

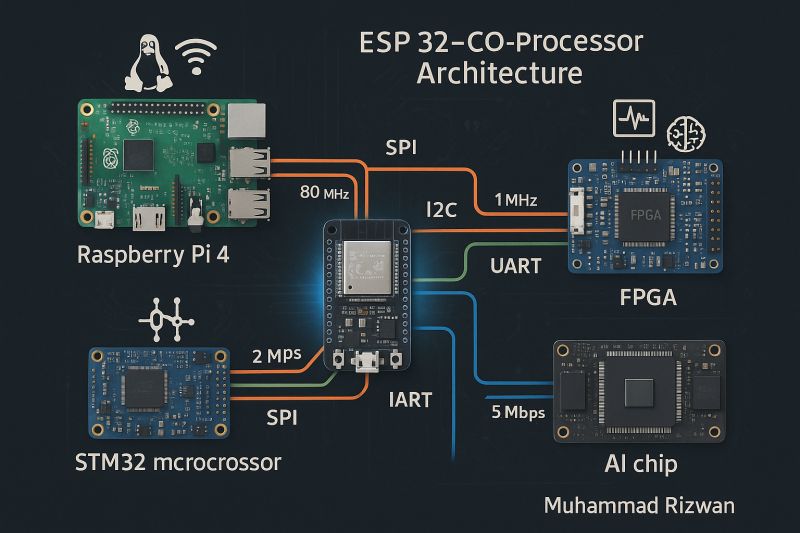

The image depicts a central ESP32 microcontroller acting as a hub, connecting to various other processing units via different communication protocols. Here's a breakdown:

- Central Hub: ESP32: Positioned centrally, the ESP32 (indicated by the title) functions as the orchestrator, connecting to other chips. It is highlighted as the ‘co-processor architecture’.

- Connected Devices:

- Raspberry Pi 4: Connected via SPI (Serial Peripheral Interface) at 80 MHz. The Raspberry Pi is a more powerful single-board computer.

- FPGA (Field Programmable Gate Array): Connected via I2C (Inter-Integrated Circuit) at 1 MHz and UART (Universal Asynchronous Receiver/Transmitter). FPGAs are highly configurable hardware.

- STM32 Microcontroller: Connected via SPI at 2 Mbps (Megabits per second). The STM32 is another popular microcontroller.

- AI Chip: Connected via IART at 5 Mbps. This implies a specialized processor designed for artificial intelligence tasks.

- Communication Protocols: SPI, I2C, UART, and IART are labeled, showing the pathways and relative data transfer speeds between the components.

- Visual Metaphor: The image utilizes a network diagram style, visually emphasizing the interconnectivity and hierarchical relationships between the different processing units. The speed labels next to each line further define the data flow constraints.

Foucauldian Genealogical Discourse Analysis

Michel Foucault’s genealogical method traces the historical development of concepts and power structures. In this context, we can examine the discourse surrounding microcontrollers and the shift towards heterogeneous processing.

- Emergence of the Microcontroller: Historically, systems were built with discrete components. The microcontroller, appearing in the 1970s, represented a shift in power – a concentration of processing capabilities into a single, programmable chip. This was a 'discursive event,' changing how systems were conceived and built.

- The Rise of Heterogeneous Architectures: The image represents a later stage in this genealogy. The ESP32 isn’t replacing other processors; it’s coordinating them. This signifies a move away from the idea of a single, all-powerful processing unit. Instead, systems are becoming comprised of specialized processing elements.

- Power/Knowledge: The selection of communication protocols (SPI, I2C, etc.) isn’t just about technical efficiency. It’s a reflection of knowledge about these protocols and the power to implement them. Those who understand these interfaces control the flow of information within the system. The speeds indicated reveal a power imbalance, as some channels have much greater bandwidth.

- Discipline and Control: The image can be viewed as an architecture of control. The ESP32, as the central hub, disciplines and manages the activities of other components. It enforces a specific order of operation.

Critical Theory

Critical Theory, concerned with exposing structures of domination, can be applied by examining the inherent biases and limitations within this architecture.

- The ESP32 as Hegemon: The ESP32 occupies a privileged position, seemingly dictating how other processors are utilized. This reflects a potential power dynamic, where the ESP32 (and the designers who chose it) impose a certain way of working on the other devices.

- Specialization and Fragmentation: The proliferation of specialized processors (AI chip, FPGA) suggests a trend towards fragmentation of functionality. This can be seen as a form of ‘division of labor’ at the hardware level. While increasing efficiency, it could also lead to dependencies and vulnerabilities. If the ESP32 fails, the entire system might become compromised.

- The 'Black Box': The specific implementations within the AI chip and FPGA are largely opaque from this high-level view. This ‘black box’ nature of these components can obscure potential biases or ethical concerns embedded within their design.

Marxist Conflict Theory

This framework focuses on class struggle and the material conditions of production. While stretching the analogy, we can see some resonances.

- Labor & Resources: Each processing unit represents a "labor force" contributing to the overall system function. The AI chip, potentially requiring significant resources (energy, specialized design), could be considered a higher-order “skilled laborer.” The STM32, being more general-purpose, might represent a “less skilled laborer.”

- Exploitation: The ESP32's control could be interpreted as a form of “exploitation” – directing the labor of other processors for its own ends (system-level functionality). The different data transfer speeds indicate that some processors are being used more intensely than others.

- Infrastructure & Capital: The entire system is built upon a foundation of infrastructure (communication protocols, power supplies). The investment in these components (capital) determines the system's capabilities.

Postmodernism

Postmodernism challenges grand narratives and embraces fragmentation and subjectivity.

- Deconstruction of Hierarchy: The image challenges the idea of a single, dominant processor. It presents a networked system where power is distributed (though not equally). This deconstructs the traditional hierarchy of computing.

- Simulation & Hyperreality: The interconnectedness and reliance on communication protocols can be seen as a form of simulation. The system's behavior isn't simply determined by its physical components but also by the rules governing their interactions.

- Loss of Foundational Truth: The modularity of the system suggests that there is no single "essential" component. The system's functionality is dependent on the interplay of different elements, blurring the lines between hardware and software.

Queer Feminist Intersectional Analysis

This framework is less directly applicable, but can be insightful if we stretch the analogy.

- Marginalization & Representation: The FPGA and AI chip, positioned somewhat peripherally in the diagram, could be seen as representing 'marginalized' components. They are dependent on the ESP32 for communication and integration.

- Intersectionality: The communication protocols themselves (SPI, I2C, etc.) represent different 'identities' or interfaces. The fact that some protocols are faster than others suggests that certain interfaces have more 'privilege' within the system.

- Fluidity & Hybridity: The image celebrates hybridity, combining different types of processors into a single system. This challenges rigid categorization and embraces fluidity.

Conclusion

The "ESP32 co-processor architecture" meme, when viewed through the lens of microcontroller theory and these diverse theoretical frameworks, reveals layers of complexity beyond a simple technical diagram. It illustrates a shift towards heterogeneous processing, raises questions about power dynamics, and highlights the inherent biases embedded within technological systems. It exemplifies how even a technical schematic can be analyzed as a complex socio-technical construct.

Disclaimer: Some of these theoretical interpretations are admittedly stretched to fit the image. The goal is to demonstrate how these frameworks can be applied to even seemingly simple technological artifacts.

simple-description (llama3.2-vision_11b)

The meme is a humorous image of a microcontroller (a small computer chip) with a "talking" face and a caption that says "I can talk, but you can't hear me". The image is likely a joke about the limitations of a microcontroller's ability to communicate with humans, and the humor comes from the absurdity of a small computer chip trying to talk to someone who can't hear it.